### Lecture 11 Parallel Processing & **Multicore computers** 8th edition: Ch 17 & 18 Earlier editions contain only Parallel Processing

Comp. Org II, Spring 2010

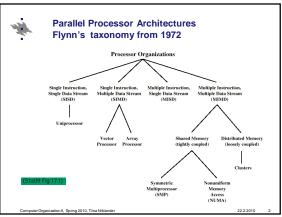

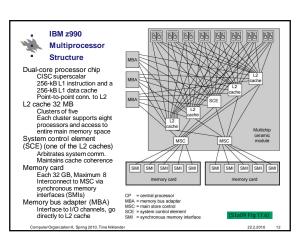

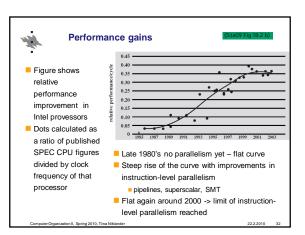

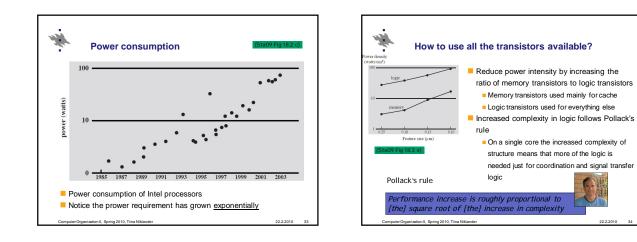

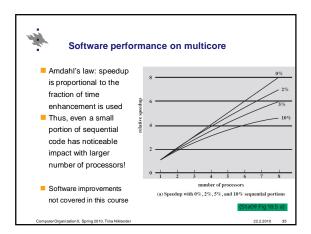

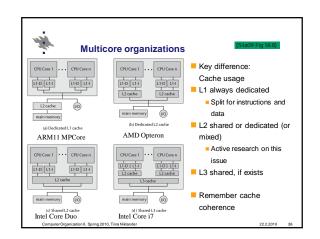

Why multicore? Current trend by processor manufacturers, because older improvements are no longer that promising Clock frequency Pipeline, superscalar, Simultaneous multithreading , SMT (or hyperthreading) Enough transistors available on one chip to put two or more whole cores on the chip Symmetric multiprocessor on one chip only But ... diminishing returns More complexity requires more logic Increasing chip area for coordinating and signal transfer logic Harder to design, make and debug

#### Comp. Org II, Spring 2010