| X86                 | (Sta09 Table 12. |                                      |                             |                  |

|---------------------|------------------|--------------------------------------|-----------------------------|------------------|

| T                   | AX, EBX, ECX, E  |                                      |                             |                  |

| Туре                | Number           | Length (bits)                        |                             | SP, EBP, ESI, ED |

| General             | 8                | 32                                   | General-purpose user regist | CS, SS, DS,      |

| Segment             | 6                | 16                                   | Contain segment selectors   | ES, FS, GS       |

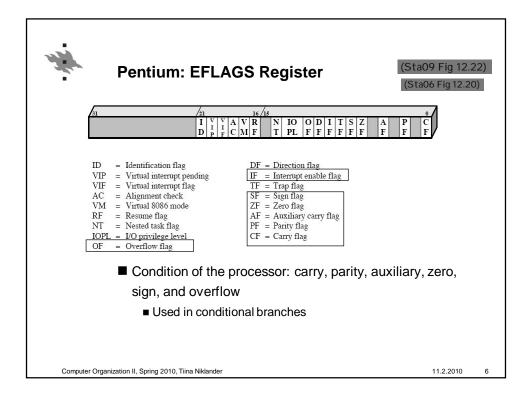

| EFLAGS              | 1                | 32                                   | Status and control bits     | L3, F3, G3       |

| Instruction Pointer | 1                | 32                                   | Instruction pointer         | EFLAGS           |

| Туре                | (b) Ir           | nteger Unit in 64-1<br>Length (bits) | Dit Mode<br>Purpose         |                  |

| General             | 16               | 32                                   | General-purpose user regist | ers              |

| Segment             | 6                | 16                                   | Contain segment selectors   |                  |

|                     |                  | 64                                   | Status and control bits     |                  |

| RFLAGS              | 1                | 04                                   | orardo and control ono      |                  |

| ×86                 | : Proces | sor Regist        | (Sta09 Table 12.                                                |

|---------------------|----------|-------------------|-----------------------------------------------------------------|

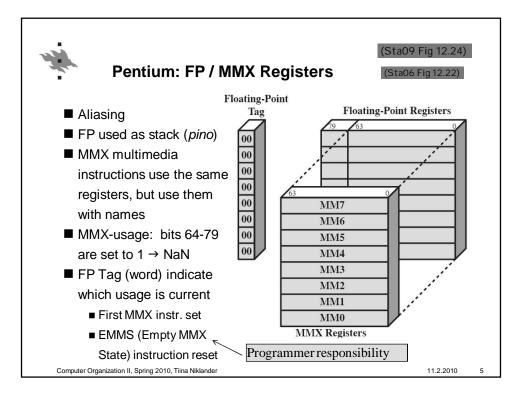

|                     | (        | c) Floating-Point | Unit Function as a stack<br>or store MMX value                  |

| Туре                | Number   | Length (bits)     | Purpose                                                         |

| Numeric             | 8        | 80                | Hold floating-point numbers                                     |

| Control             | 1        | 16                | Control bits                                                    |

| Status              | 1        | 16                | Status bits                                                     |

| Tag Word            | 1        | 16                | Specifies contents of numeric registers                         |

| Instruction Pointer | 1        | 48                | Points to instruction interrupted<br>by exception selector, off |

| Data Pointer        | 1        | 48                | Points to operand interrupted by exception                      |

| Pentium: Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                      | See Sta09 Table 12.3                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Calling interrupt handler; atomic harr<br>If not in privileged mode ( <i>etuoikeutettu</i><br>PUSH(SS) stack segment select<br>PUSH(ESP) stack pointer to stact<br>PUSH(EFLAGS) status register to<br>EFLAGS.IOPL ← 00 set privileged to<br>EFLAGS.IF ← 0 disable interrupt<br>EFLAGS.TF ← 0 disable exception<br>PUSH(CS) code segment selector<br>PUSH(EIP) instruction pointer to se<br>PUSH(error code) if needed<br>number ← interrupt controller / INT-instruction | a tila)<br>ctor to stack<br>ctor to stack<br>stack<br>mode<br>s (keskeytys)<br>ons (poikkeus)<br>or to stack<br>stack (käskyosoitin) |

| CS ← interrupt vector [number].CS                                                                                                                                                                                                                                                                                                                                                                                                                                        | Address translation:                                                                                                                 |

| EIP ← interrupt vector [number].EIP<br>■ Return                                                                                                                                                                                                                                                                                                                                                                                                                          | Segment nunber- and<br>offset from interrupt vector =>                                                                               |

| Privileged IRET-instruction                                                                                                                                                                                                                                                                                                                                                                                                                                              | Address of the interrupt handler                                                                                                     |

| POP everything from stack to their p                                                                                                                                                                                                                                                                                                                                                                                                                                     | laces                                                                                                                                |

| Computer Organization II, Spring 2010, Tiina Niklander                                                                                                                                                                                                                                                                                                                                                                                                                   | 11.2.2010 8                                                                                                                          |

| vector is | nber Description                                                                                                                                                                 |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0         | Divide error; division overflow or division by zero                                                                                                                              |

| 1         | Debug exception; includes various faults and traps related to debugging                                                                                                          |

| 2         | NMI pin interrupt; signal on NMI pin                                                                                                                                             |

| 3         | Breakpoint; caused by INT 3 instruction, which is a 1-byte instruction useful for debugging                                                                                      |

| 4         | INTO-detected overflow; occurs when the processor executes INTO with the OF flag set                                                                                             |

| 5         | BOUND range exceeded; the BOUND instruction compares a register with boundaries stored in<br>memory and generates an interrupt if the contents of the register is out of bounds. |

| 6         | Undefined opcode                                                                                                                                                                 |

| 7         | Device not available; attempt to use ESC or WAIT instruction fails due to lack of external device                                                                                |

| 8         | Double fault; two interrupts occur during the same instruction and cannot be handled serially                                                                                    |

| 9         | Reserved                                                                                                                                                                         |

| 10        | Invalid task state segment; segment describing a requested task is not initialized or not valid                                                                                  |

| 11        | Segment not present; required segment not present                                                                                                                                |

| 12        | Stack fault; limit of stack segment exceeded or stack segment not present                                                                                                        |

| 13        | General protection; protection violation that does not cause another exception (e.g., writing to a read-only segment)                                                            |

| 14        | Page fault                                                                                                                                                                       |

| 15        | Reserved                                                                                                                                                                         |

| 16        | Floating-point error; generated by a floating-point arithmetic instruction                                                                                                       |

| 17        | Alignment check; access to a word stored at an odd byte address or a doubleword stored at an address not a multiple of 4                                                         |

| 18        | Machine check; model specific                                                                                                                                                    |

| 19-3      | Reserved                                                                                                                                                                         |

|           |                                                                                                                                                                                  |

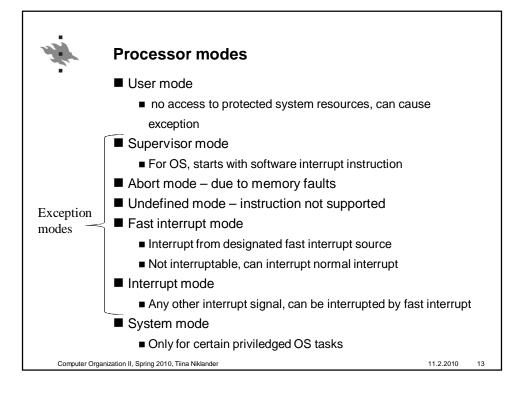

|                      |            |            |                 | Modes      |           |            |                   |  |

|----------------------|------------|------------|-----------------|------------|-----------|------------|-------------------|--|

| •                    |            |            |                 | Privilege  | ed modes  |            |                   |  |

|                      |            |            | Exception modes |            |           |            |                   |  |

| SP – stack pointer   | User       | System     | Supervisor      | Abort      | Undefined | Interrupt  | Fast<br>Interrupt |  |

| LR – link register   | R0         | R0         | R0              | R0         | R0        | R0         | R0                |  |

| PC – program counter | R1         | R1         | R1              | R1         | R1        | R1         | R1                |  |

|                      | R2         | R2         | R2              | R2         | R2        | R2         | R2                |  |

| CPSR – current       | R3         | R3         | R3              | R3         | R3        | R3         | R3                |  |

|                      | R4         | R4         | R4              | R4         | R4        | R4         | R4                |  |

| program status       | <b>R</b> 5 | R5         | R5              | R5         | R5        | R5         | <b>R</b> 5        |  |

| register             | R6         | R6         | R6              | R6         | R6        | R6         | R6                |  |

| -                    | <b>R</b> 7 | <b>R</b> 7 | <b>R</b> 7      | <b>R</b> 7 | R7        | <b>R</b> 7 | R7                |  |

| SPSR – saved         | R8         | R8         | R8              | R8         | R8        | R8         | R8_fiq            |  |

| program status       | R9         | R9         | R9              | R9         | R9        | R9         | R9_fiq            |  |

| program status       | R10        | R10        | R10             | R10        | R10       | R10        | R10_fiq           |  |

| register             | R11        | R11        | R11             | R11        | R11       | R11        | R11_fiq           |  |

| 0                    | R12        | R12        | R12             | R12        | R12       | R12        | R12_fiq           |  |

|                      | R13 (SP)   | R13 (SP)   | R13_svc         | R13_abt    | R13_und   | R13_irq    | R13_fiq           |  |

| Shaded regs replaced | R14 (LR)   | R14 (LR)   | R14_svc         | R14_abt    | R14_und   | R14_irq    | R14_fiq           |  |

| 0,                   | R15 (PC)   | R15 (PC)   | R15 (PC)        | R15 (PC)   | R15 (PC)  | R15 (PC)   | R15 (PC)          |  |

| in exception modes!  |            |            |                 | Di         | 8         | 21         |                   |  |

|                      | CPSR       | CPSR       | CPSR            | CPSR       | CPSR      | CPSR       | CPSR              |  |

|                      |            | 17         | SPSR_svc        | SPSR_abt   | SPSR_und  | SPSR_irq   | SPSR_fiq          |  |

|                                  | Exception type            | Mode       | Normal<br>entry<br>address | Description                                                                                                                                                                   |

|----------------------------------|---------------------------|------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  | Reset                     | Supervisor | 0x00000000                 | Occurs when the system is initialized.                                                                                                                                        |

| ARM Interrupt                    | Data abort                | Abort      | 0x00000010                 | Occurs when an invalid memory address<br>has been accessed, such as if there is no<br>physical memory for an address or the<br>correct access permission is lacking.          |

| vector                           | FIQ (fast interrupt)      | FIQ        | 0x000001C                  | Occurs when an external device asserts the<br>FIQ pin on the processor. An interrupt<br>cannot be interrupted except by an FIQ.<br>FIQ is designed to support a data transfer |

| Table lists the                  |                           |            |                            | or channel process, and has sufficient<br>private registers to remove the need for                                                                                            |

| exception types                  |                           |            |                            | register saving in such applications,<br>therefore minimizing the overhead of                                                                                                 |

| and the address in               |                           |            |                            | context switching. A fast interrupt cannot<br>be interrupted.                                                                                                                 |

| interrupt vector for             | IRQ (interrupt)           | IRQ        | 0x0000018                  | Occurs when an external device asserts the                                                                                                                                    |

| that type.                       |                           |            |                            | IRQ pin on the processor. An interrupt<br>cannot be interrupted except by an FIQ.                                                                                             |

| The vector                       | Prefetch abort            | Abort      | 0x000000C                  | Occurs when an attempt to fetch an<br>instruction results in a memory fault. The<br>exception is raised when the instruction<br>enters the execute stage of the pipeline.     |

| contains the start               | Undefined<br>instructions | Undefined  | 0x00000004                 | Occurs when an instruction not in the<br>instruction set reaches the execute stage of<br>the pipeline.                                                                        |

| addresses of the                 | Software interrupt        | Supervisor | 0x0000008                  | Generally used to allow user mode                                                                                                                                             |

| interrupt handlers.              |                           |            |                            | programs to call the OS. The user program<br>executes a SWI instruction with an<br>argument that identifies the function the<br>user wishes to perform.                       |

| Computer Organization II, Spring | g 2010, Tiina Niklander   |            |                            | 11.2.2010 16                                                                                                                                                                  |

| ~           |                      |              | 0            | u da sud                   | iah ar       |                    |

|-------------|----------------------|--------------|--------------|----------------------------|--------------|--------------------|

| 0           | peratio              | ons and      | Opera        | nas, wr                    | nich are     | e used?            |

| _           | V 400                | 0            |              |                            |              | 1- 00000           |

|             |                      |              |              | X, PDP-1'                  |              |                    |

| -           | Dynamic              | c, occurre   | ncies du     | ring the e                 | xecution     |                    |

|             | Dynamic (            | Occurrence   |              | Instruction<br>ghted       |              | Reference<br>ghted |

|             | Pascal               | С            | Pascal       | С                          | Pascal       | C                  |

| ASSIGN      | (45%)                | 38%          | 13%          | 13%                        | 14%          | 15%                |

| LOOP        | 5%                   | 3%           | (42%)        | 32%                        | 33%          | 26%                |

| CALL        | 15%                  | 12%          | 31%          | 33%                        | 44%          | 45%                |

| IF          | 29%                  | (43%)        | 11%          | 21%                        | 7%           | 13%                |

| GOTO        | _                    | 3%           | _            | <u> </u>                   |              | <u> </u>           |

| OTHER       | 6%                   | 1%           | 3%           | 1%                         | 2%           | 1%                 |

|             | Weighted Re          | lative Dynam | ic Frequency | y of HLL Oper              | ations [PAT] | [82a]              |

|             | Р                    | ascal C      | Average      |                            |              | 30% of reference   |

| Integer Con | nstant               | 16% 23%      | 20%          | D . D                      |              |                    |

| Scalar Vari | able 🤇               | 58% 53%      | 55%          | Dynamic Per<br>of Operands |              | o local variables  |

| Array/Strue | cture                | 26% 24%      | 25%          | 1                          |              | 06 Table 13.2, 1   |

|             |                      |              | 0.000        |                            | (518         |                    |

|             | n II, Spring 2010, T |              |              |                            |              | 11.2.2010          |

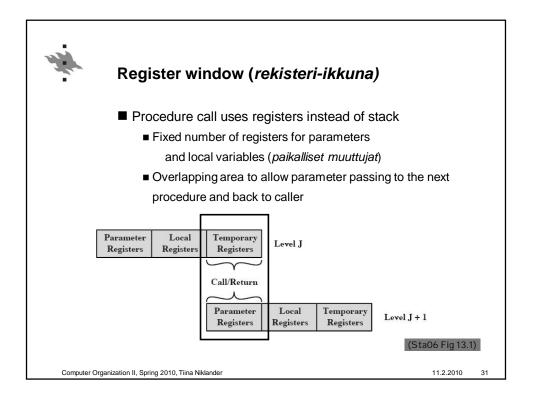

|          | Subroutine (p                                  | rocedure, functio                                     | on) calls?                     |

|----------|------------------------------------------------|-------------------------------------------------------|--------------------------------|

|          | •                                              | e calls<br>e many parameters<br>äinen) calls are rare | (Sta06 Table 13.4)             |

|          | Percentage of Executed<br>Procedure Calls With | Compiler, Interpreter, an<br>Typesetter               | d Small Nonnumeric<br>Programs |

|          | >3 arguments                                   | 0–7%                                                  | 0–5%                           |

|          | >5 arguments                                   | 0–3%                                                  | 0%                             |

|          | >8 words of arguments and local scalars        | 1-20%                                                 | 0–6%                           |

|          | >12 words of arguments and local scalars       | 1-6%                                                  | 0–3%                           |

|          | Procedu                                        | re Arguments and Local S                              | calar Variables                |

|          | How to use the                                 | information? 98% le                                   | ess than 6 parameters          |

|          |                                                |                                                       | ess than 6 local variables     |

| Computer | Organization II, Spring 2010, Tiina Niklander  |                                                       | 11.2.2010 2                    |

|                                         | Complex Instruction Set<br>(CISC)Computer |               |                | Reduced I<br>Set (RISC) |               | Superscalar |                |                |

|-----------------------------------------|-------------------------------------------|---------------|----------------|-------------------------|---------------|-------------|----------------|----------------|

| Characteristic                          | IBM<br>370/168                            | VAX<br>11/780 | Inte1<br>80486 | SPARC                   | MIPS<br>R4000 | PowerPC     | Ultra<br>SPARC | MIPS<br>R10000 |

| Year developed                          | 1973                                      | 1978          | 1989           | 1987                    | 1991          | 1993        | 1996           | 1996           |

| Number of<br>instructions               | 208                                       | 303           | 235            | 69                      | 94            | 225         |                |                |

| Instruction size (bytes)                | 26                                        | 2-57          | 1–11           | 4                       | 4             | 4           | 4              | 4              |

| Addressing modes                        | 4                                         | 22            | 11             | 1                       | 1             | 2           | 1              | 1              |

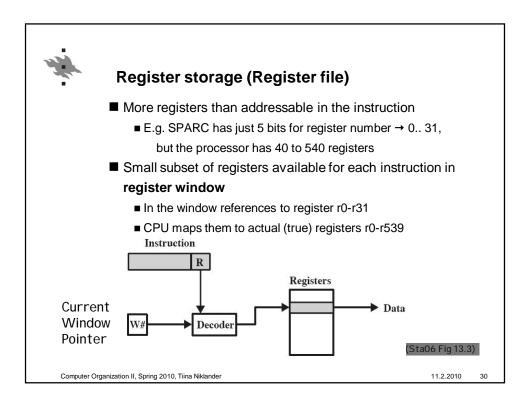

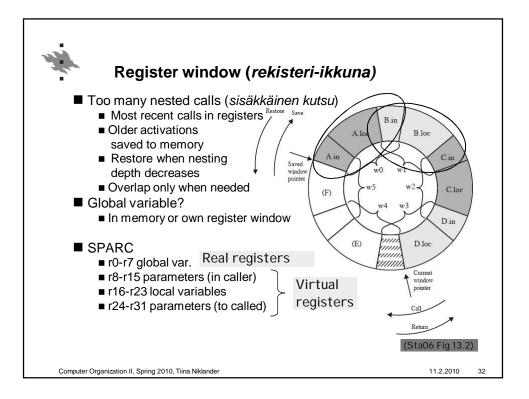

| Number of general-<br>purpose registers | 16                                        | 16            | 8              | 40 - 520                | 32            | 32          | 40 - 520       | 32             |

| Control memory size<br>(Kbits)          | 420                                       | 480           | 246            | -                       | _             | -           |                |                |

| Cache size (KBytes)                     | 64                                        | 64            | 8              | 32                      | 128           | 16-32       | 32             | 64             |

| Ch                                      | iaracteristi                              | cs of Some    | CISCs, R       | ISCs, and Sı            | ıperscalar    |             | Sta06 Tab      | le 13.1)       |

| Processor   | Number<br>of<br>instruc-<br>tion<br>sizes | Max<br>instruc-<br>tion size<br>in bytes | Number of<br>addressing<br>modes | Indirect<br>addressing | Load/store<br>combined<br>with<br>arithmetic | Ma <b>x</b><br>number of<br>memory<br>operands | Unaligned<br>addressing<br>allowed | Ma <b>x</b><br>Number of<br>MMU uses | Number of<br>bits for<br>integer<br>register<br>specifier | Number<br>bits for l<br>registe<br>specifie |

|-------------|-------------------------------------------|------------------------------------------|----------------------------------|------------------------|----------------------------------------------|------------------------------------------------|------------------------------------|--------------------------------------|-----------------------------------------------------------|---------------------------------------------|

| AMD29000    | 1                                         | 4                                        | 1                                | no                     | no                                           | 1                                              | no                                 | 1                                    | 8                                                         | 3 °                                         |

| MIPS R2000  | 1                                         | 4                                        | 1                                | no                     | no                                           | 1                                              | no                                 | 1                                    | 5                                                         | 4                                           |

| SPARC       | 1                                         | 4                                        | 2                                | no                     | no                                           | 1                                              | no                                 | 1                                    | 5                                                         | 4                                           |

| MC88000     | 1                                         | 4                                        | 3                                | no                     | no                                           | 1                                              | no                                 | 1                                    | 5                                                         | 4                                           |

| HP PA       | 1                                         | 4                                        | 10 ª                             | no                     | no                                           | 1                                              | no                                 | 1                                    | 5                                                         | 4                                           |

| IBM RT/PC   | 2ª                                        | 4                                        | 1                                | no                     | no                                           | 1                                              | no                                 | 1                                    | 4 °                                                       | 3°                                          |

| IBM RS/6000 | 1                                         | 4                                        | 4                                | no                     | no                                           | 1                                              | yes                                | 1                                    | 5                                                         | 5                                           |

| Intel i860  | 1                                         | 4                                        | 4                                | no                     | no                                           | 1                                              | no                                 | 1                                    | 5                                                         | 4                                           |

| IBM 3090    | 4                                         | 8                                        | 2 <sup>8</sup>                   | no <sup>b</sup>        | yes                                          | 2                                              | yes                                | 4                                    | 4                                                         | 2                                           |

| Intel 80486 | 12                                        | 12                                       | 15                               | no <sup>b</sup>        | yes                                          | 2                                              | yes                                | 4                                    | 3                                                         | 3                                           |

| NSC 32016   | 21                                        | 21                                       | 23                               | yes                    | yes                                          | 2                                              | yes                                | 4                                    | 3                                                         | 3                                           |

| MC68040     | 11                                        | 22                                       | 44                               | yes                    | yes                                          | 2                                              | yes                                | 8                                    | 4                                                         | 3                                           |

| VAX         | 56                                        | 56                                       | 22                               | yes                    | yes                                          | 6                                              | yes                                | 24                                   | 4                                                         | 0                                           |

| Clipper     | 4ª                                        | 8 °                                      | 9ª                               | no                     | no                                           | 1                                              | 0                                  | 2                                    | 4°                                                        | 3°                                          |

| Intel 80960 | 2ª                                        | 8 "                                      | 9ª                               | no                     | no                                           | 1                                              | yes <sup>a</sup>                   | -                                    | 5                                                         | 3°                                          |