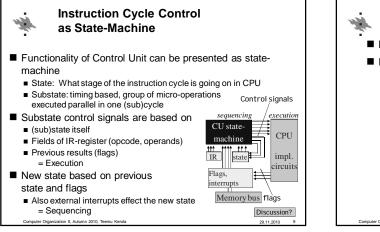

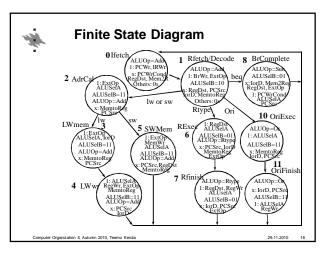

| Next state from current state | Alternatively, prior state & condition<br>S4, S5, S7, S8, S9, S11 -> State 0 |             |

|-------------------------------|------------------------------------------------------------------------------|-------------|

| State 0 -> State1             |                                                                              |             |

| State 1 -> S2, S6, S8, S10    |                                                                              | -> State1   |

| State 2 -> S5 or              |                                                                              | -> State 2  |

| State 3 -> S9 or              |                                                                              | -> State 3  |

| State 4 ->State 0             |                                                                              | -> State 4  |

| State 5 -> State 0            | State 2 & op = SW                                                            | -> State 5  |

| State 6 -> State 7            |                                                                              | -> State 6  |

| State 7 -> State 0            | State 6                                                                      | -> State 7  |

| State 8 -> <u>State 0</u>     |                                                                              | -> State 8  |

| State 9-> State 0             | State 3 & op = JMP                                                           | -> State 9  |

| State 10 -> <u>State 11</u>   |                                                                              | -> State 10 |

| State 11 -> State 0           | State 10                                                                     | -> State 11 |

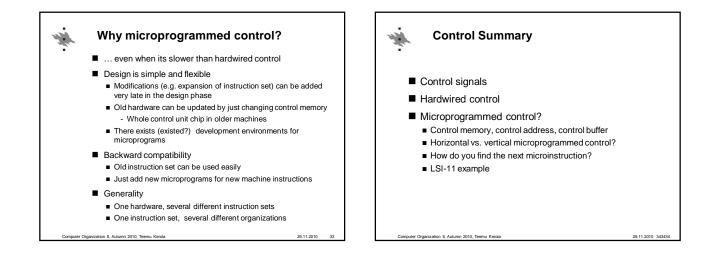

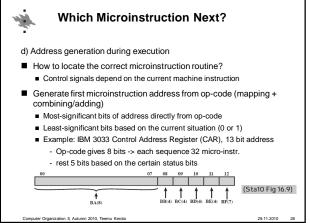

- e) Subroutines and residual control

- Microinstruction can set a special <u>return register</u> with 'return address'

- No context, just one return allowed (one-level only)

- No nested structure

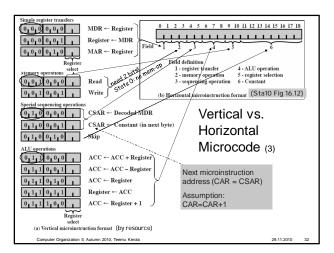

- Example: LSI-11, 22 bit microinstruction

- Control memory 2048 instructions, 11 bit address

- OP-code determines the first microinstruction address

- Assumption, next is CAR ← CAR+1

- Each instruction has a bit: subroutine call or not

- Call:

- Store return address (only the latest one available)

Jump to the routine (address in the instruction)

- Return: jump to address in return register

```

Computer Organization II, Autumn 2010, Teemu

```

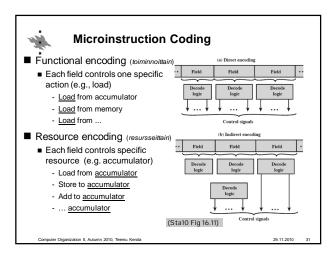

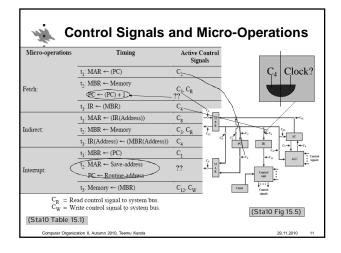

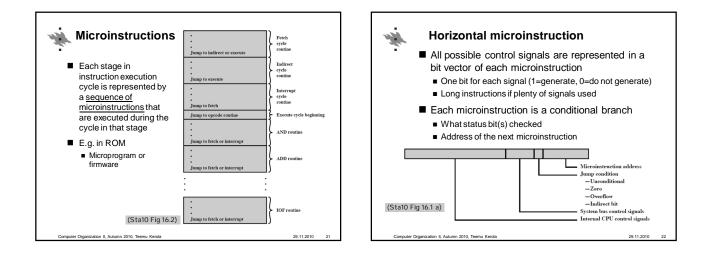

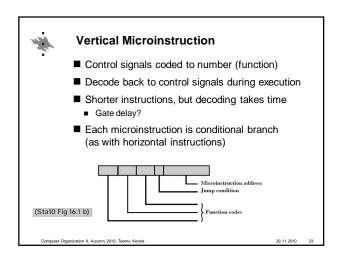

- Microinstruction split to fields, each field is used for certain control signals

- Excluding signal combinations can be coded in the same field

NOT: Reg source and destination, two sources one dest

- Coding decoded to control signals during execution

One field can control decoding of other fields!

- Several shorter coded fields easier for implementation than one long field

- Several simple decoders

omputer Organization II, Autumn 2010, Teemu Kerola

29 11 2010