#### What is Control?

- Architecture determines the CPU functionality that is visible to 'programs'

- What is the instruction set ?

- What do instructions do?

- What operations, opcodes?

- Where are the operands?

- How to handle interrupts?

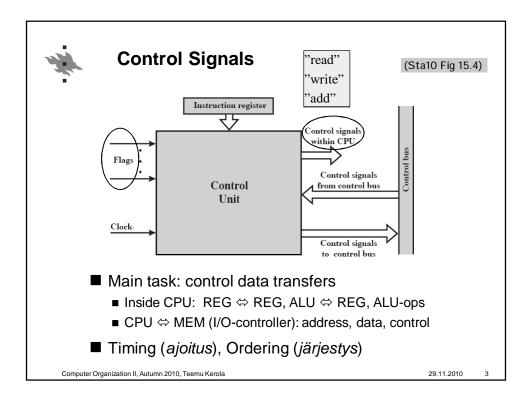

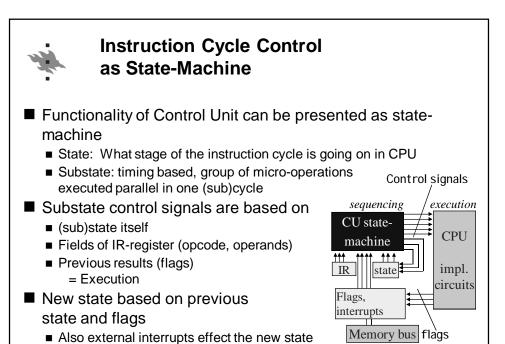

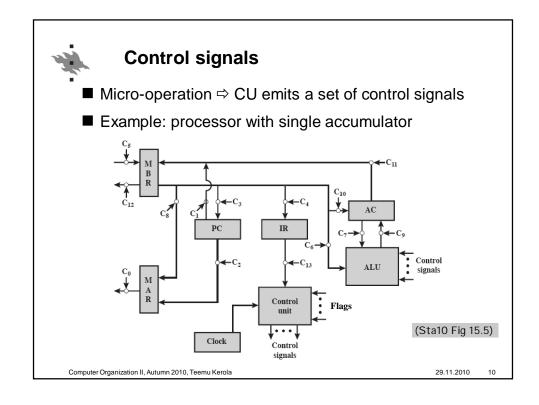

#### ■ Control Unit, CU (*ohjausyksikkö*) determines how these things happen in hardware (CPU, MEM, bus, I/O)

- What gate and circuit should do what at any given time

- Selects and gives the control signals to circuits in order

- Physical control wires transmit the control signals

- Timed by clock pulses

- Control unit decides values of the signals

Computer Organization II, Autumn 2010, Teemu Kerola

#### Functional requirements for CPU

- Operations

- Addressing modes

- Registers

- I/O module interface

- Memory module interface

- 6. Interrupt processing structure

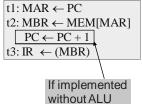

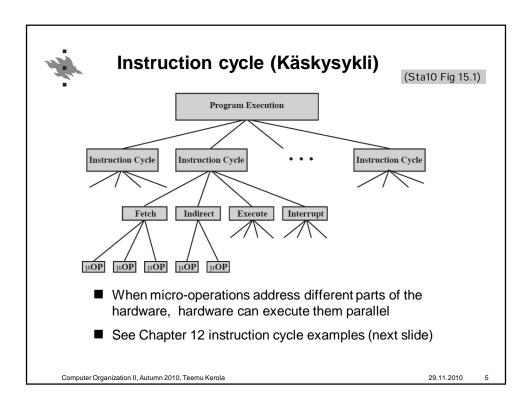

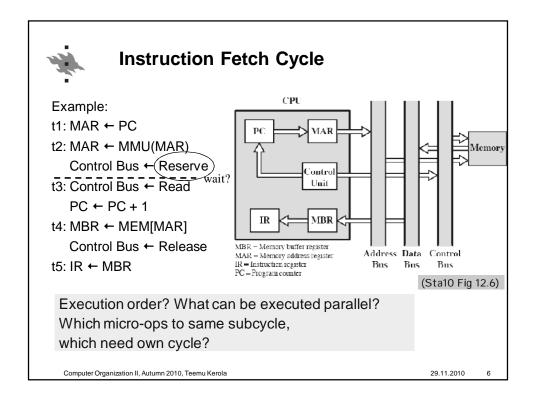

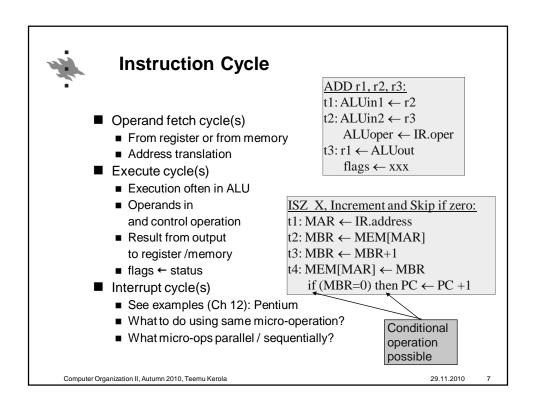

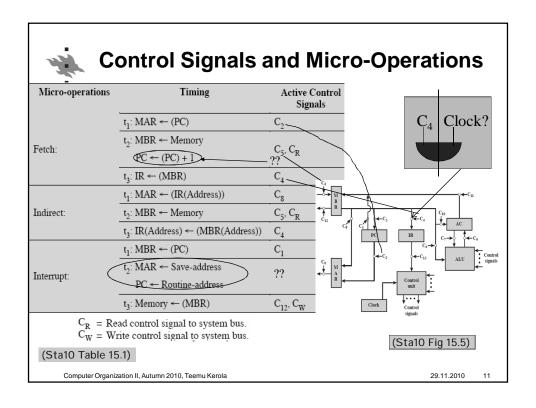

#### **Micro-Operations**

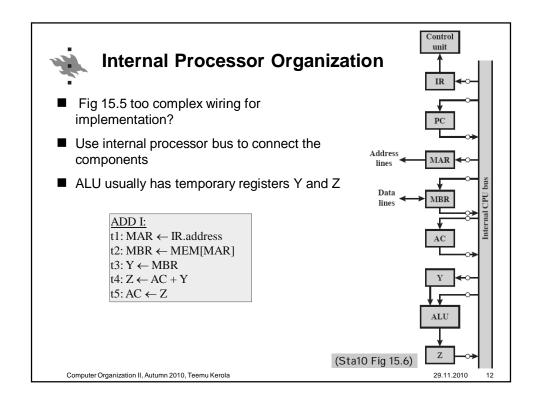

- Simple control signals that cause one very small operation (toiminto)

- E.g. Bits move from reg 1 through internal bus to ALU

- Subcycle duration determined from the longest operation

- During each subcycle multiple micro-operations in action

| TI: MAR ← PC | TI

- Some can be done simultaneously,

- If in different parts of the circuits

- Must avoid resource conflicts

- WAR or RAW, ALU, bus

- Some must be executed sequentially to maintain the semantics

29.11.2010

Computer Organization II, Autumn 2010, Teemu Kerola

Discussion?

29.11.2010

= Sequencing

Computer Organization II, Autumn 2010, Teemu Kerola

#### **Computer Organization II**

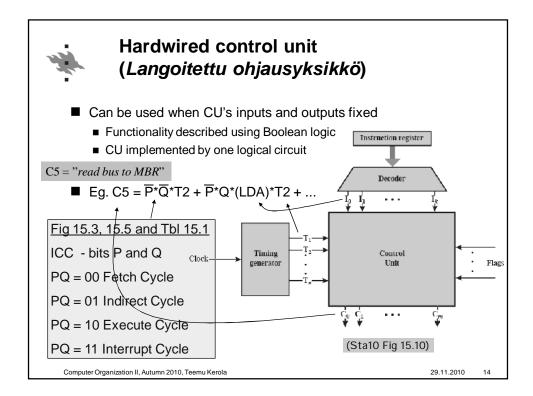

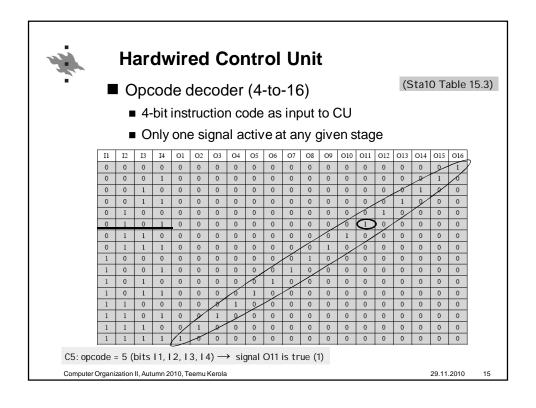

# Hardwired implementation (Langoitettu ohjaus)

Computer Organization II, Autumn 2010, Teemu Kerola

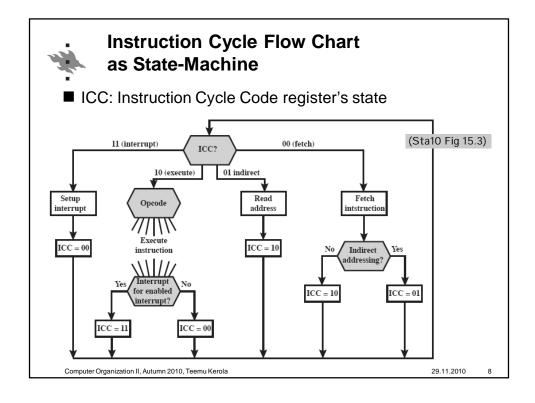

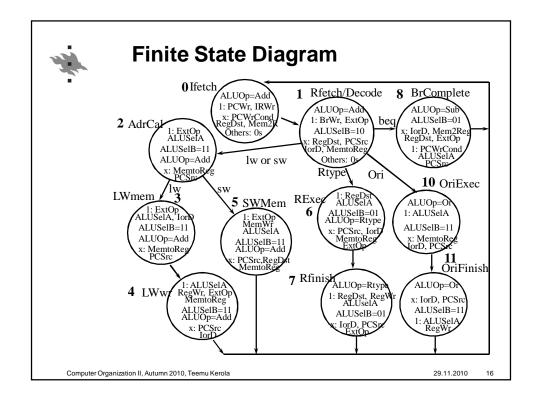

#### State transitions

#### Alternatively, prior state & condition Next state from current state S4, S5, S7, S8, S9, S11 -> State 0 State 0 -> State1 -> State1 State 1 -> S2, S6, S8, S10 -> State 2 State 2 -> S5 or ... -> State 3 State 3 -> S9 or ... -> State 4 State 4 ->State 0 State 5 -> <u>State 0</u> State 2 & op = SW -> State 5 State 6 -> State 7 -> State 6 State 7 -> State 0 State 6 -> State 7 State 8 -> State 0 -> State 8 State 9-> State 0 State 3 & op = JMP -> State 9 State 10 -> State 11 -> State 10 State 11 -> State 0 State 10 -> State 11

Computer Organization II, Autumn 2010, Teemu Kerola

29.11.2010

W.

#### **Hardwired Control Summary**

- Control signal generation in hardware is fast

- Weaknesses

- CU difficult to design

- Circuit can become large and complex

- CU difficult to modify and change

- Design and 'minimizing' must be done again after every change

- RISC-philosophy makes it a bit easier

- Simple instruction set makes the design and implementation easier

Computer Organization II, Autumn 2010, Teemu Kerola

#### **Computer Organization II**

## Microprogrammed Control (*Mikro-ohjelmoitu ohjaus*)

Computer Organization II, Autumn 2010, Teemu Kerola

11 2010

40

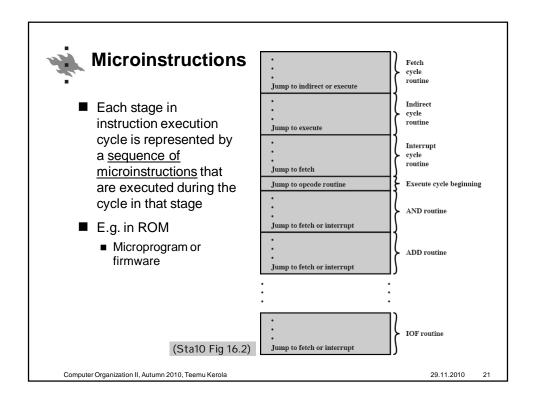

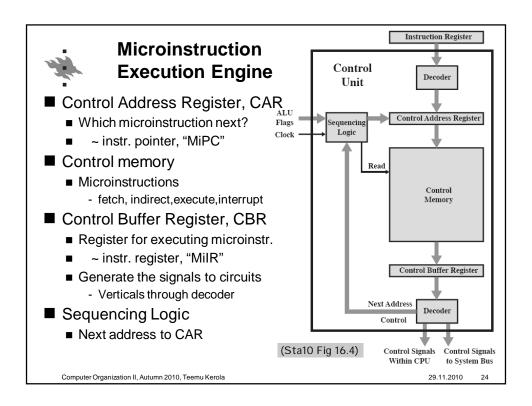

### Microprogrammed Control (Mikro-ohjelmoitu ohjaus)

- Idea 1951: Wilkes Microprogrammed Control (Maurice Wilkes)

- Execution Engine

- Execution of one machine instruction is done by executing a sequence of microinstructions (micro-operations)

- Executes each microinstruction by generating the control signals indicated by the instruction

- Micro-operations stored in <u>control memory as microinstructions</u>

- Firmware (laiteohjelmisto)

- Each microinstruction has two parts

- What is done during the coming clock cycle?

- Microinstruction indicates the control signa

- Deliver the control signals to circuits

- What/where is the next microinstruction?

- Assumption: next microinstruction from next location

- Microinstruction can contain the address of next microinstruction!

Computer Organization II, Autumn 2010, Teemu Kerola

29.11.2010

(Sta10 Fig 15.11)

Comp. Org II, Autumn 2010

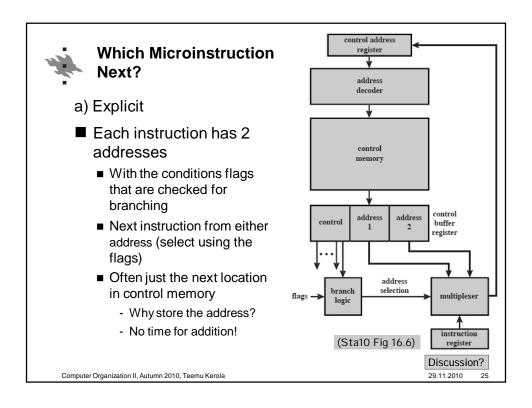

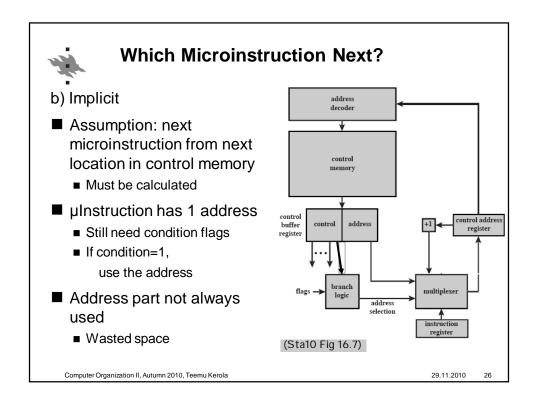

#### **Which Microinstruction Next?**

- e) Subroutines and residual control

- Microinstruction can set a special <u>return register</u> with 'return address'

- No context, just one return allowed (one-level only)

- No nested structure

- Example: LSI-11, 22 bit microinstruction

- Control memory 2048 instructions, 11 bit address

- OP-code determines the first microinstruction address

- Assumption, next is CAR ← CAR+1

- Each instruction has a bit: subroutine call or not

- Call:

- Store return address (only the latest one available)

- Jump to the routine (address in the instruction)

- Return: jump to address in return register

Computer Organization II, Autumn 2010, Teemu Kerola

29.11.2010

29

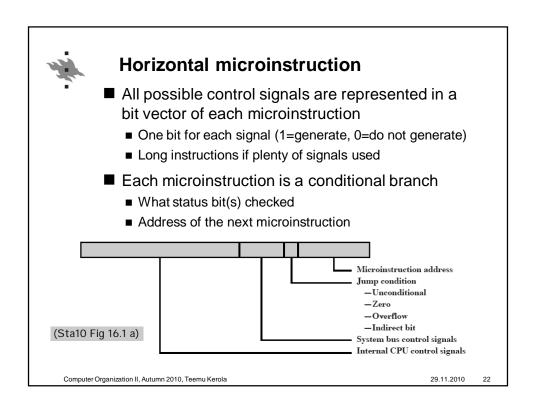

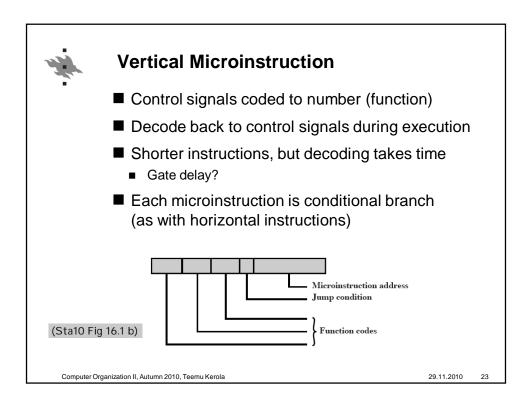

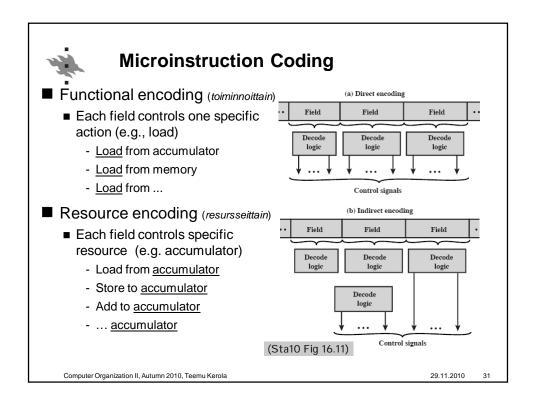

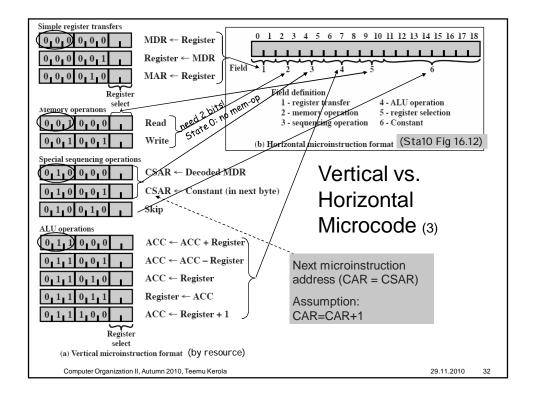

#### **Microinstruction Coding**

- Horizontal or Vertical?

- Horizontal: fast interpretation

- Vertical: less bits, smaller space

- Often a compromize, using mixed model

- Microinstruction split to fields, each field is used for certain control signals

- Excluding signal combinations can be coded in the same field

- NOT: Reg source and destination, two sources one dest

- Coding decoded to control signals during execution

- One field can control decoding of other fields!

- Several shorter coded fields easier for implementation than one long field

- Several simple decoders

Computer Organization II, Autumn 2010, Teemu Kerola

#### Why microprogrammed control?

- ... even when its slower than hardwired control

- Design is simple and flexible

- Modifications (e.g. expansion of instruction set) can be added very late in the design phase

- Old hardware can be updated by just changing control memory

- Whole control unit chip in older machines

- There exists (existed?) development environments for microprograms

- Backward compatibility

- Old instruction set can be used easily

- Just add new microprograms for new machine instructions

- Generality

- One hardware, several different instruction sets

- One instruction set, several different organizations

Computer Organization II, Autumn 2010, Teemu Kerola

29.11.2010

.

#### **Control Summary**

- Control signals

- Hardwired control

- Microprogrammed control?

- Control memory, control address, control buffer

- Horizontal vs. vertical microprogrammed control?

- How do you find the next microinstruction?

- LSI-11 example

Computer Organization II, Autumn 2010, Teemu Kerola

29.11.2010 343434

#### Review Questions / Kertauskysymyksiä

- Hardwired vs. microprogrammed control?

- How to determine the address of microinstruction?

- What is the purpose of control memory?

- Horizontal vs. vertical microinstruction?

- Compare microprogram execution to machine language fetch-execute cycle.

- Microprogrammed vs. hardwired?

Computer Organization II, Autumn 2010, Teemu Kerola