| X86                 |         | ssor Re             | (Sta10 Table 12.2                                           |

|---------------------|---------|---------------------|-------------------------------------------------------------|

|                     | . ,     | iteger Unit in 32-1 |                                                             |

| Туре                | Number  | Length (bits)       |                                                             |

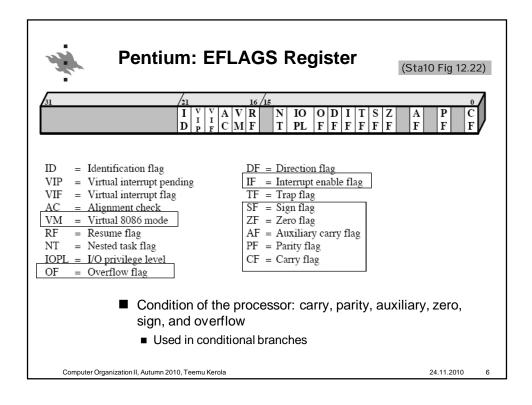

| General             | 8       | 32                  | General-purpose user registers CS, SS, DS,                  |

| Segment             | 6       | 16                  | Contain segment selectors —                                 |

| EFLAGS              | 1       | 32                  | Status and control bits ES, FS, GS                          |

| Instruction Pointer | 1       | 32                  | Instruction pointer EFLAGS                                  |

|                     | (b) In  | nteger Unit in 64-1 | EIP<br>pit Mode                                             |

| Туре                | Number  | Length (bits)       | Purpose                                                     |

| Type                |         |                     |                                                             |

| General             | 16      | 32                  | General-purpose user registers                              |

| ••                  | 16<br>6 | 32<br>16            | General-purpose user registers<br>Contain segment selectors |

| General             |         |                     |                                                             |

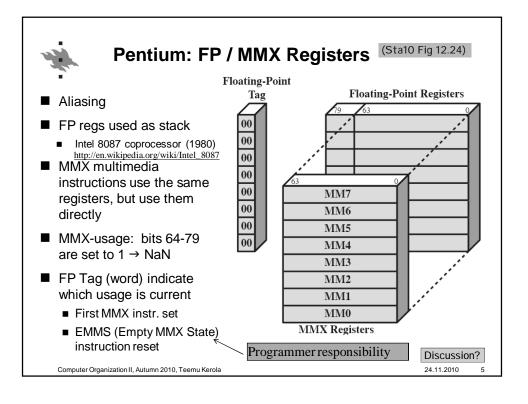

| •                   |        |                   |                                | (Sta10 Table 12.2                             |

|---------------------|--------|-------------------|--------------------------------|-----------------------------------------------|

|                     | (0     | c) Floating-Point | Unit                           | Functions as a FP stac<br>or store MMX values |

| Туре                | Number | Length (bits)     | Ι                              | Purpose                                       |

| Numeric             | 8      | 80                | Hold floating                  | -point numbers                                |

| Control             | 1      | 16                | Control bits                   | round, precis, int disable                    |

| Status              | 1      | 16                | Status bits                    | FP sp, cc, exceptions                         |

| Tag Word            | 1      | 16                | Specifies con<br>registers     | tents of numeric<br>fp, mmx, emmx             |

| Instruction Pointer | 1      | 48                | Points to inst<br>by exception | ruction interrupted For<br>exception          |

| Data Pointer        | 1      | 48                | Points to oper<br>exception    | rand interrupted by handler<br>support        |

| Vector Number | Description                                                                                                                                                                      |  |  |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 0             | Divide error; division overflow or division by zero                                                                                                                              |  |  |  |  |  |  |

| 1             | Debug exception; includes various faults and traps related to debugging                                                                                                          |  |  |  |  |  |  |

| 2             | NMI pin interrupt; signal on NMI pin Nonmaskable interrupt                                                                                                                       |  |  |  |  |  |  |

| 3             | Breakpoint; caused by INT 3 instruction, which is a 1-byte instruction useful for debugging                                                                                      |  |  |  |  |  |  |

| 4             | INTO-detected overflow; occurs when the processor executes INTO with the OF flag set                                                                                             |  |  |  |  |  |  |

| 5             | BOUND range exceeded; the BOUND instruction compares a register with boundaries stored in<br>memory and generates an interrupt if the contents of the register is out of bounds. |  |  |  |  |  |  |

| 6             | Undefined opcode                                                                                                                                                                 |  |  |  |  |  |  |

| 7             | Device not available; attempt to use ESC or WAIT instruction fails due to lack of external device                                                                                |  |  |  |  |  |  |

| 8             | Double fault; two interrupts occur during the same instruction and cannot be handled serially                                                                                    |  |  |  |  |  |  |

| 9             | Reserved                                                                                                                                                                         |  |  |  |  |  |  |

| 10            | Invalid task state segment; segment describing a requested task is not initialized or not valid                                                                                  |  |  |  |  |  |  |

| 11            | Segment not present; required segment not present                                                                                                                                |  |  |  |  |  |  |

| 12            | Stack fault; limit of stack segment exceeded or stack segment not present                                                                                                        |  |  |  |  |  |  |

| 13            | General protection; protection violation that does not cause another exception (e.g., writing to a read-only segment)                                                            |  |  |  |  |  |  |

| 14            | Page fault                                                                                                                                                                       |  |  |  |  |  |  |

| 15            | Reserved                                                                                                                                                                         |  |  |  |  |  |  |

| 16            | Floating-point error; generated by a floating-point arithmetic instruction                                                                                                       |  |  |  |  |  |  |

| 17            | Alignment check; access to a word stored at an odd byte address or a doubleword stored at an address not a multiple of 4                                                         |  |  |  |  |  |  |

| 18            | Machine check; model specific                                                                                                                                                    |  |  |  |  |  |  |

| 19-31         | Reserved                                                                                                                                                                         |  |  |  |  |  |  |

|               | User interrupt vectors; provided when INTR signal is activated Maskable interrupt                                                                                                |  |  |  |  |  |  |

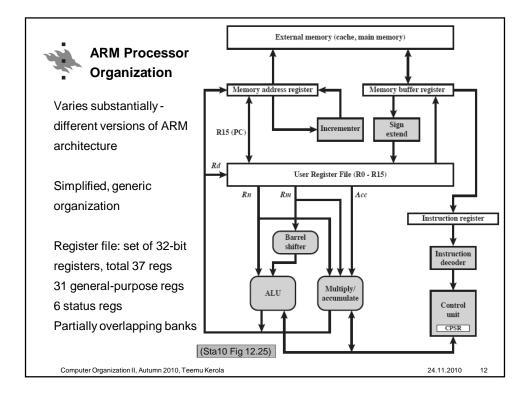

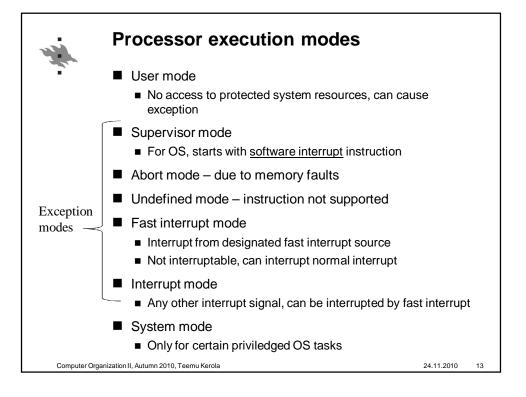

|                                      |               |            |            | Modes      |              |            |                   |

|--------------------------------------|---------------|------------|------------|------------|--------------|------------|-------------------|

| ARM                                  |               |            |            | Privilege  | d modes      |            |                   |

| Register<br>organization             |               |            |            |            | xception mod |            |                   |

| -                                    | User          | System     | Supervisor | Abort      | Undefined    | Interrupt  | Fast<br>Interrupt |

| SP – stack pointer                   | R0            | R0         | R0         | R0         | R0           | R0         | R0                |

| LR – <u>link register</u>            | R1            | R1         | R1         | R1         | R1           | R1         | R1                |

| (return address&mode)                | R2            | R2         | R2         | R2         | R2           | R2         | R2                |

| PC – program counter                 | R3            | R3         | R3         | R3         | R3           | R3         | R3                |

|                                      | R4            | R4         | R4         | R4         | R4           | R4         | R4                |

| CPSR – current                       | R5            | R5         | R5         | R5         | R5           | R5         | R5                |

| program status register              | R6            | R6         | R6         | R6         | R6           | R6         | R6                |

| SPSR – saved                         | <b>R</b> 7    | <b>R</b> 7 | <b>R</b> 7 | <b>R</b> 7 | <b>R</b> 7   | <b>R</b> 7 | <b>R</b> 7        |

| program status register              | R8            | R8         | R8         | R8         | R8           | R8         | R8_fiq            |

| 1 - 3 3 3                            | R9            | R9         | R9         | R9         | R9           | R9         | R9_fiq            |

|                                      | R10           | R10        | R10        | R10        | R10          | R10        | R10_fiq           |

| Shaded regs replaced                 | R11           | R11        | R11        | R11        | R11          | R11        | R11_fiq           |

| in exception modes!                  | R12           | R12        | R12        | R12        | R12          | R12        | R12_fiq           |

|                                      | R13 (SP)      | R13 (SP)   | R13_svc    | R13_abt    | R13_und      | R13_irq    | R13_fiq           |

|                                      | R14 (LR)      | R14 (LR)   | R14_svc    | R14_abt    | R14_und      | R14_irq    | R14_fiq           |

|                                      | R15 (PC)      | R15 (PC)   | R15 (PC)   | R15 (PC)   | R15 (PC)     | R15 (PC)   | R15 (PC)          |

|                                      |               |            |            |            |              |            |                   |

|                                      | CPSR          | CPSR       | CPSR       | CPSR       | CPSR         | CPSR       | CPSR              |

|                                      |               |            | SPSR_svc   | SPSR_abt   | SPSR_und     | SPSR_irq   | SPSR_fiq          |

| (Sta10 Fig 12.26)                    |               |            |            |            |              | -          | cussion?          |

| Computer Organization II, Autumn 201 | 0, Teemu Kero | la         |            |            |              | 24.11      | .2010 14          |

|                                                                                                          | Exception type                        | Processor<br>Mode | Normal<br>entry<br>address | Description                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                          | Reset                                 | Supervisor        | 0x00000000                 | Occurs when the system is initialized.                                                                                                                                                                                                                                                                                                                                                                                |

| ARM Interrupt                                                                                            | Data abort                            | Abort             | 0x00000010                 | Occurs when an invalid memory address<br>has been accessed, such as if there is no<br>physical memory for an address or the<br>correct access permission is lacking.                                                                                                                                                                                                                                                  |

| vector<br>Table lists the<br>exception types<br>and the address in<br>interrupt vector for<br>that type. | FIQ (fast interrupt)                  | FIQ               | 0x000001C                  | Occurs when an external device asserts the<br>FIQ pin on the processor. An interrupt<br>cannot be interrupted except by an FIQ.<br>FIQ is designed to support a data transfer<br>or channel process, and has sufficient<br>private registers to remove the need for<br>register saving in such applications,<br>therefore minimizing the overhead of<br>context switching. A fast interrupt cannot<br>be interrupted. |

|                                                                                                          | IRQ (interrupt)                       | IRQ               | 0x0000018                  | Occurs when an external device asserts the<br>IRQ pin on the processor. An interrupt<br>cannot be interrupted except by an FIQ.                                                                                                                                                                                                                                                                                       |

| The vector<br>contains the start<br>addresses of the                                                     | Prefetch abort                        | Abort             | 0x000000C                  | Occurs when an attempt to fetch an<br>instruction results in a memory fault. The<br>exception is raised when the instruction<br>enters the execute stage of the pipeline.                                                                                                                                                                                                                                             |

| interrupt handlers.                                                                                      | Undefined<br>instructions             | Undefined         | 0x00000004                 | Occurs when an instruction not in the instruction set reaches the execute stage of the pipeline.                                                                                                                                                                                                                                                                                                                      |

|                                                                                                          | Software interrupt (Sta10 Table 12.4) | Supervisor        | 0x0000008                  | Generally used to allow user mode<br>programs to call the OS. The user program<br>executes a SWI instruction with an<br>argument that identifies the function the<br>user wishes to perform.                                                                                                                                                                                                                          |

| Computer Organization II, Autum                                                                          | n 2010, Teemu Kerola                  |                   |                            | 24.11.2010 16                                                                                                                                                                                                                                                                                                                                                                                                         |

|            | p -        | - all      |               | a open         |               | Are Used                 |  |  |

|------------|------------|------------|---------------|----------------|---------------|--------------------------|--|--|

| ►<br>■ Ye  | ar 1982 o  | comput     | ers VAX I     | PDP-11, N      | lotorola 6    | 58000                    |  |  |

|            |            |            |               |                |               |                          |  |  |

| Ob         | serve dyr  | namic e    | execution t   | ime behav      | lour          |                          |  |  |

|            |            |            | Machine       | -Instruction   | Memory        | Reference                |  |  |

|            | Dynamic (  | Occurrenc  | e We          | eighted        | Wei           | ighted                   |  |  |

|            | Pascal     | C          | Pascal        | С              | Pascal        | С                        |  |  |

| ASSIGN     | 45%        | 38%        | 13%           | 13%            | 14%           | 15%                      |  |  |

| LOOP       | 5%         | 3%         | (42%)         | 32%            | 33%           | 26%                      |  |  |

| CALL       | 15%        | 12%        | 31%           | 33%            | 44%           | 45%                      |  |  |

| IF         | 29%        | 43%        | ) 11%         | 21%            | 7%            | 13%                      |  |  |

| GOTO       | _          | 3%         | -             | _              | -             |                          |  |  |

| OTHER      | 6%         | 1%         | 3%            | 1%             | 2%            | 1%                       |  |  |

|            | Weighted R | elative Dy | namic Frequen | cy of HLL Oper | -             | -                        |  |  |

|            | р          | ascal      | C Average     | (HLL=High      | n Level Langu | age)                     |  |  |

| T C        |            |            |               |                |               | 80% of referen           |  |  |

| Integer Co |            |            | 3% 20%        | Dynamic Pe     | 0             | to <u>local</u> variable |  |  |

| Scalar Var | iable 🤇    |            | 3% 55%        | of Operands    | 5             |                          |  |  |

| Array/Stru | cture      | 26% 24     | 4% 25%        |                | (Sta          | a10 Table 13.2, 13       |  |  |

| Subroutine (p                                   | procedure, func                          | tion) calls?                 |

|-------------------------------------------------|------------------------------------------|------------------------------|

| Lots of subroutine                              | calls                                    |                              |

| Calls rarely have r                             | many parameters                          |                              |

| Nested (sisäkkäine                              | en) calls are rare                       | (Sta10 Table 13.4)           |

| Percentage of Executed<br>Procedure Calls With  | Compiler, Interpreter, and<br>Typesetter | Small Nonnumeric<br>Programs |

| >3 arguments                                    | 0–7%                                     | 0-5%                         |

| >5 arguments                                    | 0-3%                                     | 0%                           |

| >8 words of arguments and local scalars         | 1–20%                                    | 0–6%                         |

| >12 words of arguments and local scalars        | 1-6%                                     | 0–3%                         |

| Procedu                                         | re Arguments and Local Scal              | lar Variables                |

| 98% less than 6 paramet                         | ers                                      |                              |

| 92% less than 6 local var                       | iables                                   |                              |

| How to use the in                               | formation?                               |                              |

| uter Organization II, Autumn 2010, Teemu Kerola |                                          | 24.11.201                    |

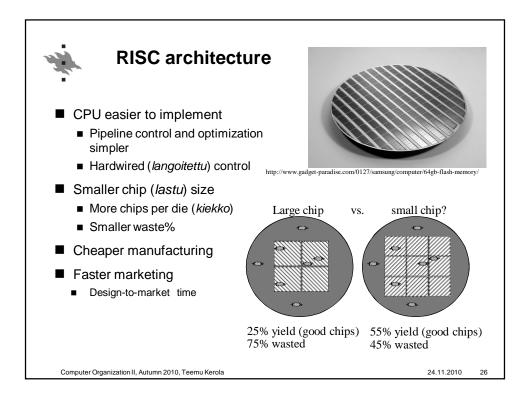

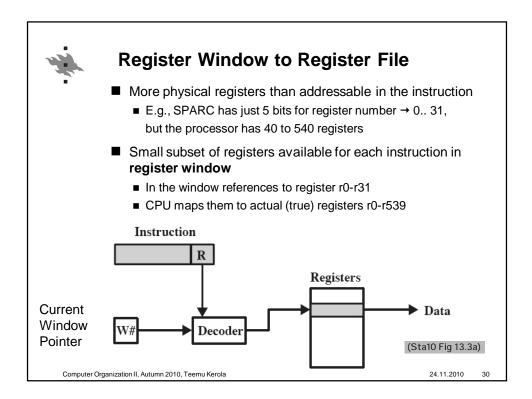

| 370/168       11/780       80486       R4000       SPARC       R10000         'ear developed       1973       1978       1989       1987       1991       1993       1996       1996         iumber of<br>istructions       208       303       235       69       94       225                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         |              | lex Instructi<br>ISC)Compu |          | Reduced I<br>Set (RISC) | nstruction<br>Computer | Superscalar |          |                |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------|----------------------------|----------|-------------------------|------------------------|-------------|----------|----------------|--|

| Jumber of<br>Isstructions         208         303         235         69         94         225            Instruction size (bytes)         2-6         2-57         1-11         4         4         4         4         4           Inderessing modes         4         22         11         1         1         2         1         1           Iumber of general-<br>urpose registers         16         16         8         40 - 520         32         32         40 - 520         32           Scontrol memory size<br>(Kbits)         420         480         246         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                   | Characteristic                          |              |                            |          | SPARC                   |                        | PowerPC     |          | MIPS<br>R10000 |  |

| Instructions         Instruction size (bytes)         2-6         2-57         1-11         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4         4 <td>Year developed</td> <td>1973</td> <td>1978</td> <td>1989</td> <td>1987</td> <td>1991</td> <td>1993</td> <td>1996</td> <td>1996</td> | Year developed                          | 1973         | 1978                       | 1989     | 1987                    | 1991                   | 1993        | 1996     | 1996           |  |

| indexessing modes         4         22         11         1         1         2         1         1           induces of general-<br>umpose registers         16         16         8         40 - 520         32         32         40 - 520         32           iontrol memory size<br>Kbits)         420         480         246         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         <                                                                                                                    | Number of<br>instructions               | 208          | 303                        | 235      | 69                      | 94                     | 225         |          |                |  |

| Imper of general-<br>umpose registers         16         16         8         40 - 520         32         32         40 - 520         32           control memory size<br>Kbits)         420         480         246         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -<                                                                                                                     | Instruction size (bytes)                | 2-6          | 2-57                       | 1–11     | 4                       | 4                      | 4           | 4        | 4              |  |

| Impose registers         420         480         246         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                                    | Addressing modes                        | 4            | 22                         | 11       | 1                       | 1                      | 2           | 1        | 1              |  |

| Kbits)         64         64         8         32         128         16-32         32         64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Number of general-<br>purpose registers | 16           | 16                         | 8        | 40 - 520                | 32                     | 32          | 40 - 520 | 32             |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Control memory size<br>(Kbits)          | 420          | 480                        | 246      | -                       | _                      | -           | _        | -              |  |

| Characteristics of Some CISCs, BISCs, and Superscelar Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Cache size (KBytes)                     | 64           | 64                         | 8        | 32                      | 128                    | 16-32       | 32       | 64             |  |

| Characteristics of Some CiSes, Rises, and Superscalar Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Cl                                      | naracteristi | cs of Some                 | CISCs, R | ISCs, and St            | iperscalar             | Processors  |          |                |  |

| Processor   | Number<br>of<br>instruc-<br>tion<br>sizes | Ma <b>x</b><br>instruc-<br>tion size<br>in bytes | Number of<br>addressing<br>modes | Indirect<br>addressing | Load/store<br>combined<br>with<br>arithmetic | Ma <b>x</b><br>number of<br>memory<br>operands | Unaligned<br>addressing<br>allowed | Max<br>Number of<br>MMU uses | Number of<br>bits for<br>integer<br>register<br>specifier | Number of<br>bits for FP<br>register<br>specifier |

|-------------|-------------------------------------------|--------------------------------------------------|----------------------------------|------------------------|----------------------------------------------|------------------------------------------------|------------------------------------|------------------------------|-----------------------------------------------------------|---------------------------------------------------|

| AMD29000    | 1                                         | 4                                                | 1                                | no                     | no                                           | 1                                              | no                                 | 1                            | 8                                                         | 3 °                                               |

| MIPS R2000  | 1                                         | 4                                                | 1                                | no                     | no                                           | 1                                              | no                                 | 1                            | 5                                                         | 4                                                 |

| SPARC       | 1                                         | 4                                                | 2                                | no                     | no                                           | 1                                              | no                                 | 1                            | 5                                                         | 4                                                 |

| MC88000     | 1                                         | 4                                                | 3                                | no                     | no                                           | 1                                              | no                                 | 1                            | 5                                                         | 4                                                 |

| HP PA       | 1                                         | 4                                                | 10 <i>ª</i>                      | no                     | no                                           | 1                                              | no                                 | 1                            | 5                                                         | 4                                                 |

| IBM RT/PC   | 2ª                                        | 4                                                | 1                                | no                     | no                                           | 1                                              | no                                 | 1                            | 4 °                                                       | 3 °                                               |

| IBM RS/6000 | 1                                         | 4                                                | 4                                | no                     | no                                           | 1                                              | yes                                | 1                            | 5                                                         | 5                                                 |

| Intel i860  | 1                                         | 4                                                | 4                                | no                     | no                                           | 1                                              | no                                 | 1                            | 5                                                         | 4                                                 |

| IBM 3090    | 4                                         | 8                                                | 2 <sup>b</sup>                   | no <sup>b</sup>        | yes                                          | 2                                              | yes                                | 4                            | 4                                                         | 2                                                 |

| Intel 80486 | 12                                        | 12                                               | 15                               | no <sup>b</sup>        | yes                                          | 2                                              | yes                                | 4                            | 3                                                         | 3                                                 |

| NSC 32016   | 21                                        | 21                                               | 23                               | yes                    | yes                                          | 2                                              | yes                                | 4                            | 3                                                         | 3                                                 |

| MC68040     | 11                                        | 22                                               | 44                               | yes                    | yes                                          | 2                                              | yes                                | 8                            | 4                                                         | 3                                                 |

| VAX         | 56                                        | 56                                               | 22                               | yes                    | yes                                          | 6                                              | yes                                | 24                           | 4                                                         | 0                                                 |

| Clipper     | 4°                                        | 8 ª                                              | 9ª                               | no                     | no                                           | 1                                              | 0                                  | 2                            | 4 °                                                       | 3°                                                |

| Intel 80960 | 2ª                                        | 8 ª                                              | 9 <i>°</i>                       | no                     | no                                           | 1                                              | yes <sup>a</sup>                   | -                            | 5                                                         | 3 °                                               |

|                 | _ |   | _  | _    |       |   | _   | Forget dependency                |

|-----------------|---|---|----|------|-------|---|-----|----------------------------------|

| $\frown$        | 1 | 2 | 3  | 4    | 5     | 6 | 7   | problem here,                    |

| 100 LOAD X, rA  | Ι | E | D  |      |       |   |     | concentrate on jump!             |

| 101 ADD 1, rA   |   | I | E  |      | le? ← |   |     | concentrate on jump.             |

| 102 JUMP 105    |   |   | Ι  | E    |       |   |     | Traditional pipeline             |

| 103 ADD rA, rB  |   |   |    | Ι    | E     |   |     | clear pipeline                   |

| 105 STORE rA, Z |   |   |    |      | I     | E | D   | 1                                |

|                 |   |   |    |      |       |   |     | 1                                |

| 100 LOAD X, rA  | I | E | D  | D 11 |       |   |     | RISC with inserted NOOP          |

| 101 ADD 1, rA   |   | Ι | E  | Bubb | le?   |   |     | Two port MEM                     |

| 102 JUMP 106    |   |   | Ι  | E    |       |   |     |                                  |

| 103 NOOP        |   |   |    | Ι    | E     | _ |     | No need to clear pipeline (NOOP) |

| 106 STORE rA, Z |   |   |    |      | Ι     | E | D   |                                  |

|                 |   |   |    |      |       |   |     |                                  |

| 100 LOAD X, Ar  | Ι | E | D, |      | Τ     |   | ٦   | RISC with reversed instructions  |

| 101 JUMP 105    |   | Ι | Е  | X    |       |   |     | Use of delay slot                |

| 102 ADD 1, rA   |   |   | Ι  | ₹ E  |       |   | 1 \ | What if conditional branch?      |

| 105 STORE rA, Z |   |   |    | Ι    | E     | D | 1   | JZERO 105, rA                    |

|                 |   | - |    |      |       |   |     | (need ADD 1,rA result before     |